This is worked with by how each FPGA logic cell will, in general, include both a LUT and a register, which makes registering the output very simple.īe that as it may, these two technologies vary in more than one way, including their purpose and capacity. Having said this, basically to raise (or keep up with) execution, FPGA designs will, in general, be more profoundly pipelined than their ASIC counterparts. Indeed, a LUT can address several logic levels, so the position isn’t exactly pretty much as crucial as it might appear from the get-go. By examination, if this kind of configuration were executed on an FPGA with every one of the gates implemented in a different LUT, it would “fly like a block” on the grounds because the track delays on FPGAs are considerably more critical, somewhat talking. This implies that ASIC architects can sometimes be a little messy regarding something like this contingent upon the design. By examination, FPGA architects are more likely to instantiate explicit low-level cells.Ī Group of gates can be put together near one another in ASIC to such an extent that their track delays are minor.

#Fpga lut circuit code

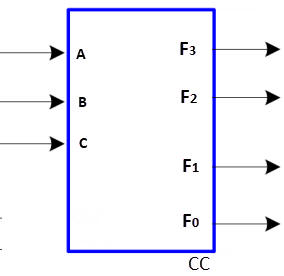

Regarding language-driven design flows, ASIC designers will generally compose entirely compact code (in VHDL or Verilog) and utilize minimum instantiated (explicitly named) cells. They comprise arrays of logic cells that can be customized utilizing a hardware description language. FPGAs and ASICS are comparative in their circuit design flow. FPGAs, organized ASICs, and ASICs are all part of the custom logic continuum.įPGAs and ASICs are the two kinds of integrated circuits frequently thought about while executing electronic product design. With regards to hardware design, system architects have a few kinds of custom logic solutions for browsing. Hardware acceleration, particularly in the form of custom logic, is helping in this regard to meet the increasing needs for performance, lower power, and lower total cost of ownership.įor example, 5G demands higher clock rates within a limited power budget in high-bandwidth wireless services.

In this era of wireless communication, cloud computing, and AI, enormous demands on computing platforms are continuously placed.

We may not see the makers of these advances battling on the NYSE floor, not yet, at any rate, it doesn’t imply that there is no aggravation (loss of pay). In the realm of hardware, there are conflicts as well, viz., between operating systems, gaming consoles, and even chip development (FPGA versus ASIC).

0 kommentar(er)

0 kommentar(er)